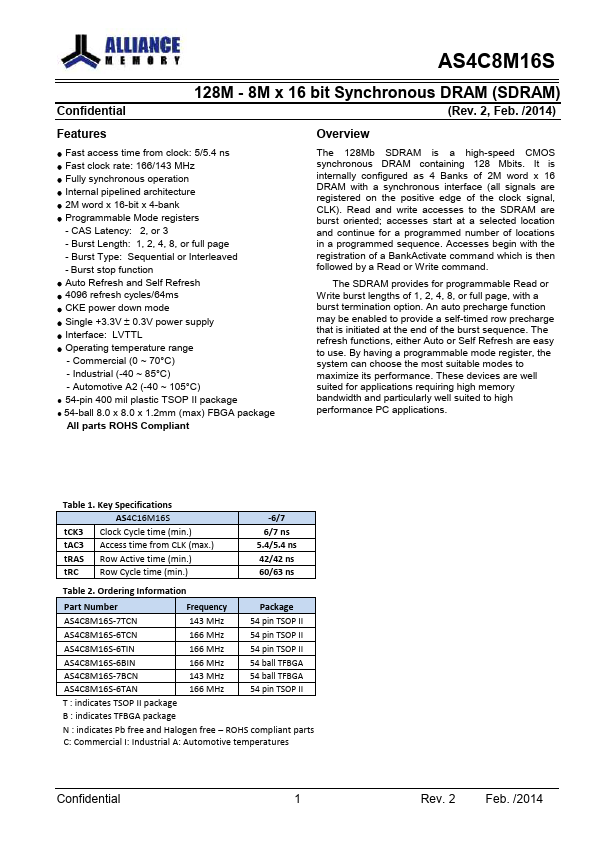

AS4C8M16S Overview

Key Specifications

Package: TSOP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Key Features

- CAS Latency: 2, or 3 - Burst Length: 1, 2, 4, 8, or full page

- Burst Type: Sequential or Interleaved

- Burst stop function

- Auto Refresh and Self Refresh

- 4096 refresh cycles/64ms